Chip Services

Chip Services

Products

Products

- Automotive and Industrial control

- Information Security

- Edge Computing& Network Communication

Products

Resources

Resources

Language

Language

CCM3310S-H is designed based on the 32-bit security CPU CS0 with independent intellectual property rights. It is distinguished by low power consumption, high performance, multifunction and high security level. It can be widely applied in trusted computing, online banking, mobile payment, data security, secure communication, copyright control, and other fields.The chip’s typical operating frequency is 100MHz.

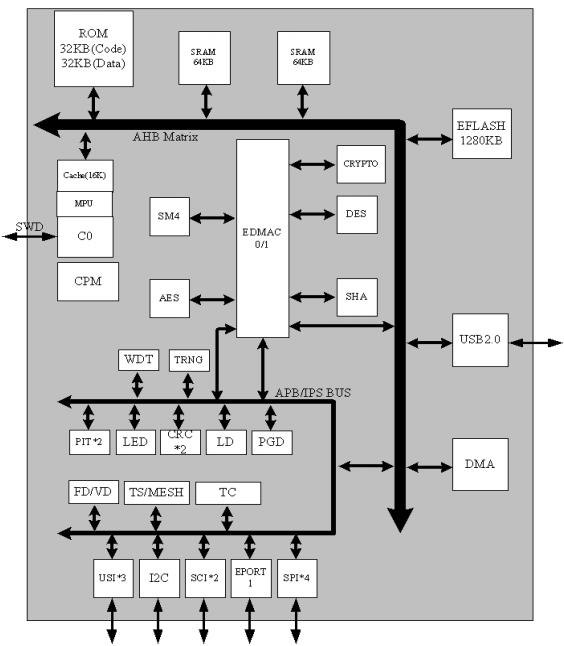

Block diagram of CCM3310S-H

Package Type

| Pin | Package type and pin assignment(mm) | |

QFN32(5*5) | QFN40(5*5) | |

SPI(Multiplexing) | 2 | 2 |

I2C | 1 | 1 |

SCI | 1 | 1 |

ISO7816 | 0 | 1 |

USB | 0 | 1 |

EPORT(Multiplexing) | 2 | 4 |

● 32-bit low-power RISC core with highly optimized 3-stage pipeline

● Supporting byte, half-word, and word memory access

● Supporting interrupt nesting

● Supporting single-cycle 32-bit x 32-bit hardware integer multiplier array, 3 to13 cycle hardware integer frequency divider array

● Memory protection unit (MPU)

● Low power consumption and high performance

● Supporting cache

● Timing module EPT

● 128 K bytes of SRAM

● 64K bytes of ROM

● 1280K byte EFLASH

- 512 bytes/page

- minimum 100,000 erase cycles

● DMA/EDMA

● 2 timers (PIT)

● Watchdog (WDT)

● Time counter(TC)

● Asymmetric algorithms

- 1024bit RSA

- 2048bit RSA

- 256bit SM2 prime domain

● Symmetric algorithms

- DES/3DES supports ECB/CBC mode

- AES supports ECB/CTR mode

- SM4 supports ECB/CBC/CFB/OFB modes

● Hashing algorithms

- SM3

- SHA-0/ SHA-1/ SHA-224/ SHA-256/ SHA-384/ SHA-512

● CRC

- Supporting CRC32/ CRC16/ CRC8

- Supporting DMAC operation

● Memory protection mechanism

- Application-oriented memory partitioning with hardware support for secure isolation

- Bus scrambling

● True random number generator, compliant with FIPS 140-2 standards and national commercial cryptography standards

● Safety detection and protection unit

- Voltage detection unit

- Light detection unit

- Power supply burr detection unit

- Metal shielding protection

- Temperature detection unit

- Frequency detection unit

- Clock and reset pulse filtering

- Optimizing wire routing for security

● Supporting fingerprint algorithm acceleration function

● Unique serial number for each product

● Main power input voltage: 1.62V~3.63V

● Typical power consumption: 30mA @ 100MHz, low-power PowerOff2 mode less than 2uA

● ESD:2KV

● Supporting internal power-on reset and external reset

● Level II of security chip for commercial Crypto product certification

● EAL5+ of China Cybersecurity Review Technology and Certification Center

● Trusted computing

● Video security

● Complete development environment

● Rich driver libraries

● Complete application solutions